Large-Scale Interposer Technology as PCB Substitute in Cryogenic Particle Physics Experiments

NPSS Student Paper Award Recipient, 2022

The nEXO experiment search for neutrino-less double beta decay (0vββ) has concluded, in 2018, that it would not be possible to use PCBs in the detector. The background decay contribution from the PCB material would prevent reaching the experiment’s required sensitivity. The electronegative impurities released in the liquid xenon that quench electron lifetime also disqualify the use of PCB inside the experiment.

The goal of our project is to create a silicon equivalent to a standard Printed Circuit Board (PCB) for specialized applications like cryogenic particle physics experiments such as nEXO.

Interposers are generally used to increase signal density in electronic systems assembled in 2.5D/3D. Based on the maturity of fabrication techniques, silicon interposers have been used by the industry for nearly 15 years. The industry’s needs of high bandwidth and high density also opened the door to low-loss substrate materials like glass, fused silica, borosilicate, sapphire and more.

However, many of these technologies offer only a small size (~10 cm2) interposer and few redistribution layers. We therefore undertook the development of a suitable silicon interposer technology, with the collaboration of TRIUMF (Canada), and Fraunhofer IZM (Berlin). In the following we describe the design, the fabrication, and resulting interposers.

Requirements

Taking nEXO’s requirements as an example, the interposer technology must meet these requirements:

200 mm wafer from the first fabrication run with multiple test structures to extract technology performance.

I. Operate at cryogenic temperature: 85 K to 165 K depending on the noble gas used.

II. Very-low radioactive background contribution in the experiment’s zone of interest (Th, U, K).

III. Tile size above 5 × 5 cm2 to provide a reasonably sized unit to tile the large area experiment (e.g., Fig. 1).

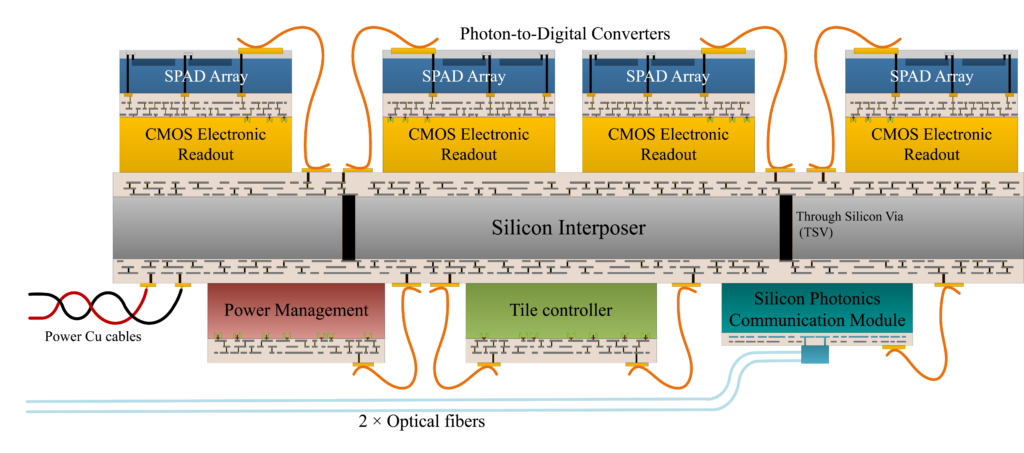

IV. Mechanically self-supporting, holding photo¬detector (SiPM or PDC) and readout electronics (e.g., Fig. 2)

Side view of Sherbrooke’s proposed PhotoDetection Module for the construction of large area photodetector planes

V. Maintain signal integrity (analog and digital) over the tile.

VI. Support 10 years of continuous operation.

Interposer Architecture

Based on Fraunhofer IZM’s knowhow, an architecture was defined to meet the requirements listed above. The use of tested technology blocs allowed us to reduce fabrication risks.

A silicon substrate was an obvious choice when compared with glass and fused silica for these reasons:

I. Maturity of micro/nanofabrication on silicon.

It offers more possibilities and potentially a higher fabrication yield.

II. High-resistivity substrate option.

In passive interposer technology, the semiconductor properties are parasitic to the circuit. However, high-resistivity wafers are available which reduce RF losses.

III. Matched Coefficient of Thermal Expansion (CTE) with the Si-based integrated circuits.

By sharing the same CTE as the bare photodetectors and readout electronics, the induced thermal stress is minimized which benefits detector reliability and lifetime.

IV. Radiopurity.

Silicon used in the nanofabrication industry is a good material in terms of radiopurity because of low concentrations of K, Th and U. Final products still need to be assayed to reach stringent background requirements.

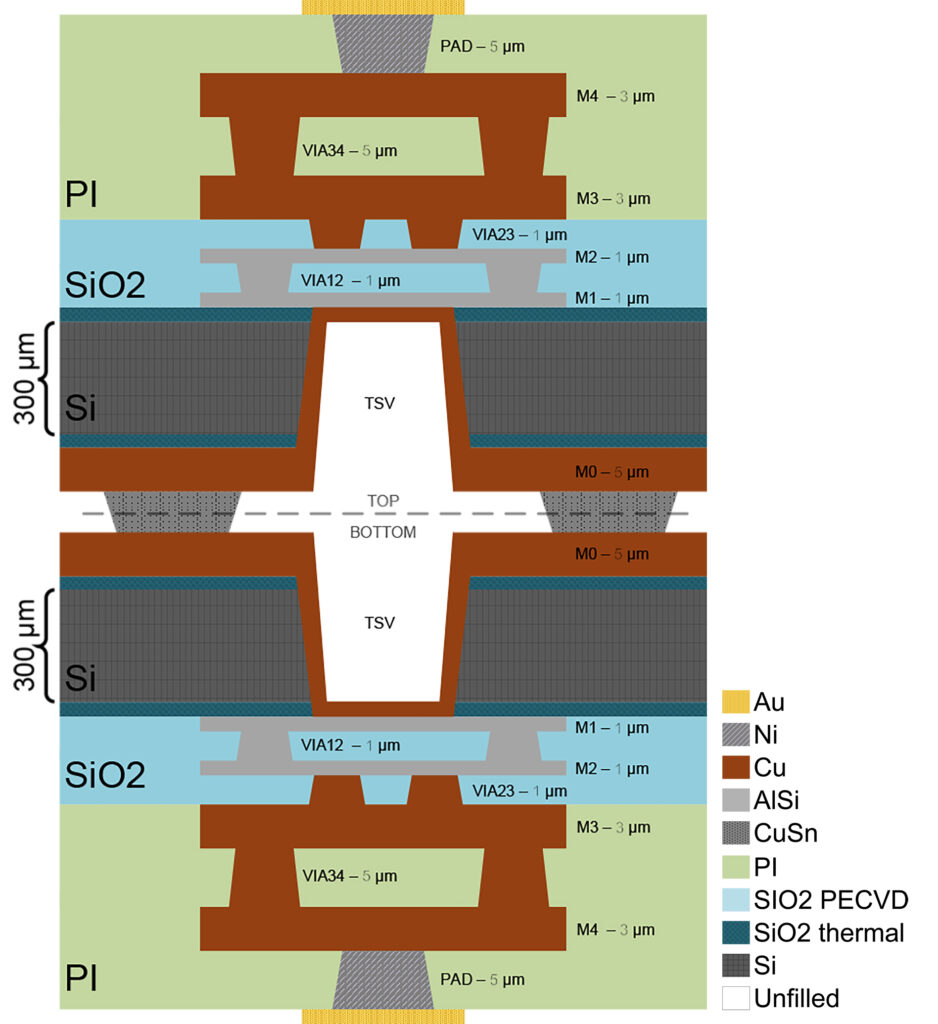

From the beginning of the project, we estimated that four redistribution layers (RDL) on each side of the interposer should allow for a sufficiently complex routing scheme. Furthermore, the technology must have Through Silicon Vias (TSVs) to allow interconnects between both sides of the interposer. For example, this is key to connect photodetectors on top of the interposer with the electronics on the bottom.

To solve many fabrication issues, we decided to form the interposer out of two silicon wafers of identical structure.

First, by doing so, the global architecture becomes symmetric, thereby providing the best immunity to deformation due to residual thin film stresses.

Second, a good structural integrity can be achieved while minimizing each wafer’s thickness. This is crucial for the TSV-last process we use because it reduces the TSV depth, easing fabrication and reducing TSV diameter (maintaining a low TSV depth-to-diameter ratio).

Third, as seen in Fig. 3, the TSVs are annular and empty causing important challenges to further microfabrication steps on the back side of each wafer. By reducing the number of fabrication steps on the back side to only the bonding CuSn layer, we hope to increase the yield.

10 layers silicon interposer architecture. Both wafers have identical structures.

Lastly, because both wafers have the same structure, they can be processed simultaneously even if they don’t have the same circuit patterns.

With the use of two different dielectrics, PECVD SiO2 and spin-coated Polyimide (PI), it was possible to form four redistribution layers: two layers of 3-µm-thick Cu separated by 0.5-µm PI with two layers of 1-µm-thick AlSi separated by 1-µm of SiO2. In the middle of the interposer (i.e., between both wafers), two layers of 5-µm of Cu are available for TSV interconnects and signal routing. The two wafers are bonded with CuSn pads. Having multiple materials and thickness enables features like power mesh decoupling, 50 ohms coplanar transmission lines, low-resistive analog lines, etc. The objective is to give to circuit designers a versatile technology to be used in multiple applications.

First Production Run And Results

A first lot of 25 wafers was fabricated by Fraunhofer IZM between 2019 and 2021. Since this architecture is new, multiple process splits occurred during the fabrication to validate the fabrication and optimize the parameters.

The wafers from this first fabrication phase were characterized at the Interdisciplinary Institute for Technological Innovation of the Université de Sherbrooke. Technology performances like sheet resistivity, dielectric leakage, via resistivity, layer capacitance and more were extracted from the measurements. We have included them in the CAD technology kit to enable a second run of design and fabrication with more precise material details. It also allows distributing to collaborators.

An impressive achievement in this project is that the fabrication was successful on its first fabrication phase. This confirms our choices of relying on known technology blocs. From the 25 wafers, 21 were delivered, and the four remaining wafers were used at the IZM foundry for destructive inspection.

Future Work: Second Production Run

From the various physical inspections and electrical characterization during the project’s first phase, a few improvements will be made to the architecture and the fabrication recipes:

Substrate thickness will be reduced to 250 µm to reduce TSV diameter and ease fabrication.

The integrity of the dielectric layer between the first two metal layers to increase the yield of highly overlapped structures.

To evaluate the impact of these improvements, a second production run will occur. The second production run will contain fewer test structures and demonstrate its functionality as a large-scale interposer by interfacing multiple photodetectors (PDCs and SiPMs) and connecting them to either readout circuits or cables and connectors.

IEEE NSS-MIC-RTSD 2022: A Thrilling Experience

With the financial support of NSERC and the IEEE, I was able to attend the IEEE NSS-MIC RTSD 2022 in person. I’m grateful for the child support I received for the conference which made this professional experience all the more possible. This opportunity to meet colleagues in my field of work was a wonderful experience. I am grateful that I was selected to present my project in an oral presentation in the NSS Analog and Digital Circuits session. A special thanks to the jury that selected me for the IEEE Best Student Paper Award 2022 which gave me the opportunity to write this article for the prestigious NPSS newsletter.

Research Group: Grams

The GRAMS research group is led by Professors Jean-François Pratte, Serge Charlebois, Réjean Fontaine, Marc-André Tétrault, Audrey Corbeil-Therrien, and Jean-Baptiste Michaud. GRAMS includes over 70 undergraduate interns, graduate students, postdoctoral students and the scientific staff. Our expertise is the design of Application Specific Integrated Circuits (ASIC), the design, fabrication, and characterization of single-photon detectors (Photon-to-Digital Converter – PDC) [1], the development of time-to-digital converters (TDC), and FPGA implementation. We devote our expertise to medical imaging, particle physics experiments, high-energy particle detection and quantum communication. The GRAMS is as always open to collaboration and devoted student application. Please don’t hesitate to reach out at the email address at the end of the article.

Acknowledgments

The author, Keven Deslandes, a Ph.D. student in Electrical Engineering, and a member of the GRAMS, expresses his thanks to the following:

- Pr Jean-François Pratte as a research director and a mentor. Professor at Université de Sherbrooke.

- Professor Serge Charlebois as a research director and a mentor. Professor at Université de Sherbrooke.

- Dr Fabrice Retière as a loyal project collaborator. Senior Scientist at TRIUMF.

- nEXO Collaboration to support this work as a potential candidate for the photodetection module.

- NSERC for funding this project through research grants and scholarship.

- FRQNT for funding this project through scholarship.

- McDonald Canadian Astroparticle Physics Research Institute for providing tools, training, and research grants.

- Canadian Funds for Innovation for funding this project through research grants.

- IEEE for providing a trainee grant and a child support grant at IEEE NSSMIC RTSD 2022 in Milan.

The research group can be reached by E-mail at [email protected]

Reference

[1] J.-F. Pratte et al., “3D Photon-To-Digital Converter for Radiation Instrumentation: Motivation and Future Works”, Sensors, vol. 21, no. 2, p. 598, 2021.